新一代低功耗功率管理IC

摘要: 飞兆半导体公司新推出的FSEZ1317集成有许多新技术,如:内建高压启动电路、待机时的低工作频率、工作电压与工作电流,并采用初级端调节方法降低次级端反馈线路等,利用这些新技术FSEZ1317不但可以符合CEC以及能源之星的节能规范之外,待机功耗更可降低至小于30mW,符合手机充电器的新待机节能规范最高五星级的标识星号,成为新一代低待机功耗电源管理IC的最佳选择。

在全球环保意识越来越强的趋势下,更加高效地利用能源已成为全球的共识,于是近年来电子产品及其电源开始受到节能法规的限制,如美国加州能源委员会(California Energy Commission, CEC)节能规范,以及“能源之星(Energy Star)”标识计划等。但除了这些节能规范之外,另一项受到注目的新规范即是”待机功耗”。根据统计,电子产品在待机时的功耗占全球的电力3%~13%,因此在待机时的功耗也制订出明确的规范。其中在今年由五家手机大厂公布的新手机充电器的待机规范,明确定义出不同的待机功耗有不同的标识星号,由此可见,低待机功耗的电源供应器将成为下一个世代的所必须配备的基本要求。飞兆半导体公司新推出的FSEZ1317集成有许多新技术,如:内建高压启动电路、待机时的低工作频率、工作电压与工作电流,并采用初级端调节方法降低次级端反馈线路等,利用这些新技术FSEZ1317不但可以符合CEC以及能源之星的节能规范之外,待机功耗更可降低至小于30mW,符合手机充电器的新待机节能规范最高五星级的标识星号,成为新一代低待机功耗电源管理IC的最佳选择。

简介

回顾去年的石油价格飙涨,以及全球的金融危机,使得节能的议题再度获得关注,对于有效的利用能源变成是全球的共识,于是近年来电子产品的电源供应器开始受到节能法规的限制,如美国加州能源委员会(California Energy Commission, CEC)节能规范,以及能源之星(Energy Star)标识计划等,但这些电源的规范当中,最近受到注目的新规范即是”待机功耗”的规范。由于许多电子产品在插头接上的那一刻便开始有功率消耗,即使大多时间都处在待机状态,这样的待机功耗,根据统计,占全球的电力3%~13%,因此从2001年7月起美国政府机构已经明确的要求电器产品待机功耗不能超过1W。这些新的节能规范不单只是规范电源在不同负载时所需的平均效率,还定义在待机时的最低功耗,如表一所示为能源之星的效率规范与待机功耗。其中令人注目的是在今年由五家手机大厂公布的新手机充电器的待机规范,明确的定义出不同的待机功耗有不同的标识星号,如表二所示为新手机充电器的待机功耗,其中最高五颗星的待机功耗必须降低至30mW以下,由此可见,在不久的未来电源转换器低待机功耗将成为基本要求,也是电源设计工程师必须面临的挑战,而能降低待机功耗的电源芯片更是未来的需求。

表一、能源之星的规范要求 (Energy Star EPS V2.0, 2008)

表二、全新充电器功耗规范

待机功耗的来源分析与低待机功耗的解决方案:FSEZ1317

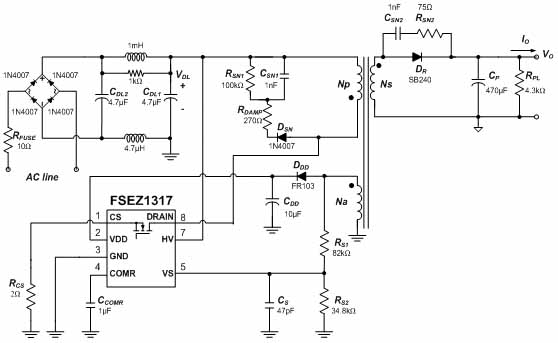

对于目前的电源系统来说,如何能从目前低于0.3W的待机功耗降低到30mW。首先可以分析一个传统反激式电源架构的每个器件,在待机时主要的损耗来源,如图一为40W的电路图,其中此电路的在230Vac的待机功耗为110mW,图二为待机损耗的分析结果

图一、40W的Flyback电路图

图二、待机功耗各部份的损耗分析图

如图二看出主要的待机功耗可以分为五种:

1、启动电阻的损耗(56%):为了使PWM IC在电源启动时能获得适时的启动,通常会有启动电设置,即在PWM IC获得启动电压之后,启动电路便失去作用。但实际上,启动电阻上的电压却不少,占待机功耗的不少比例,如何能用高压启动线路减少这类的损耗是PWM IC所需的功能之一。

2、EMI 滤波电容放电电阻(15%):为了快速释放EMI 滤波电容上的电压,在大功率电源设计上都会增加并联的放电电阻,但若针对小功率电源设计,此滤波电容放电电阻可以不采用。

3、主环路的开关组件损耗(13%):为了使输出电压为稳定的电压,PWM IC必须控制主开关的占空比与开关频率,但在待机时为了降低主开关MOSFET、变压器、次级输出整流二极管,输出假负载的损耗,因此PWM IC也在待机时适时地降低占空比与开关频率。因此如何设计在待机时的PWM讯号也是PWM IC所需的功能之一。

4、PWM IC的待机消耗(9%):在待机时为了使PWM IC维持正常的工作,在线路上必须设计合适的辅助供电,如何使PWM IC

在待机时以较低的电压和工作电流运行,以降低PWM IC的待机功耗,这也是PWM IC未来所需的功能之一。

5、次级反馈电路的待机功耗(4%):为了侦测次级的讯号,次级反馈回路需要一个合适的分压电阻网络,它的损耗占了约4%的待机功耗,若考虑一个低瓦数的应用,若能采用初级侦测的方式,此部分的待机功耗也可以减少。

从上述的五点中,其中有四点挑战是可以藉由电源芯片的功能来提升,因此通过电源芯片的控制技术使整体效能提升、成本降低之外也降低待机功耗,为绿色能源提供一个新的方向。

实际设计的一个3.5W的手机充电器,输出规格的定义为5V/0.7A。电源控制芯片采用飞兆半导体的FSEZ1317,此电源芯片在手机充电器的应用中提供极低的待机功耗,这是由于内建500V的高压启动电路,在电源IC达到启动电压之后,此电路即为开路的状态,以降低启动线路的功耗;为了降低待机功耗,绿色功能模块通过关断时间调制在轻载的时候线性降低开关频率,在空载的时候降至370Hz的最低频率,同时减少内部所需的工作电流与电压的范围,利用以上的新技术可以轻易满足絕大部分功耗要求。除此之外,崭新的核心技术采用初级端调节控制方法(PSR),利用侦测辅助绕组上的电压波形,达到控制输出端为恒定电压与恒定电流,因此不仅可以大幅的减少次级的反馈线路也减少次级端的功耗以及所需的成本。芯片包装更采用SOP8的包装与 内建700V的高压MOSFET,因此可以省掉MOSFET的走线,更可以减少零件数量,节省空间。自动恢复的保护功能包含输出短路保护(OSP)、VDD过电压保护(OVP)与过热保护(OTP)等。一个内建的Frequency Hopping功能更进一步改善EMI的性能;此外,IC还具有线损补偿功能,根据输出电流补偿输出线的压降来改善负载调整率。如图三为FSEZ1317的3.75W线路图。

图三、FSEZ1317 3.75W的应用现路图

图四、待机功耗在不同输入电压时的特性 图五、输出电压与电流特性图

图六、效率曲线图

如图四为在不同交流输入电压中的待机功耗,由图中可知即便是在264Vac的电压输入,待机功耗仍然可以低于30mW,满足最新低待机功耗手机电源规范中的最好的五星等级要求。从图五的输出电压电流曲线中,可以看出在通用交流电压的输入之下,输出端的恒定电压调节率可以达到1.38%;而当返回电压(fold-back voltage)为1.5V时,输出端的恒定电流调节率可以达到3.6%,其中在恒电流的范围中的输出电压是藉由5V~24V VDD的电压控制且在输出电压越来越低时仍然可以稳定恒定输出电流。如图六可示,平均效率可以达到71.61%@115V 与70.01%@230V,可以轻易符合”能源之星”2.0 等级五的能源规范(平均效率为65.5%的规范),为大量生产的偏差提供足够的裕度。

电源管理IC的新挑战:低待机功耗

着眼全球关注绿色能源的开发,能源效率大幅提升能帮助降低电源的损耗,集成功率芯片在电源管理中扮演一个提升效率的重要角色,它帮助电源设计降低整体的成本、开关损耗与改善EMI性能以达到“轻薄短小”的目标。本文介绍一个内置高压启动电路与降低空载时开关频率的低待机功耗电源芯片FSEZ1317,此芯片通过新颖的初级端反馈控制技术减少二次侧反馈回路的损耗。相比之下,传统的自激式转换器(Ringing Choke Converter, RCC)方案,不仅零件多、成本高,且设计复杂与制造困难,渐渐的不能符合现今的电源规范。飞兆半导体的集成电源芯片FSEZ1317方案减少了元件数目,降低成本和简化了设计,将会是低待机功耗、高效率充电器应用的最佳解决方案。

暂无评论