FPGA和TFT彩屏液晶的便携示波器设计方案

摘要: 本文针对实际需要,设计了以FPGA为核心采集模块,以单片机为显示控制核心,以TFT彩屏液晶为显示器件的便携数字存储示波器。FPGA与高速A/D获取波形采样数据,通过单片机完成彩屏的初始化,合理设计出单片机与FPGA通信的总线握手协议,配合异步FIFO作为数据缓冲模块,实现了边采集边显示的效果。

在现代通信、雷达和航空航天等应用领域,由于设备复杂度和集成度的不断增加,在进行外场维护和测试时,通常需要借助于示波器等一些辅助的电子测量仪器来观察信号的波形并进行相关参数的测量。目前,现代化的数字存储示波器以其独特的优势逐步取代了模拟示波器,对信号的测量带来了很大的便利。然而,外场测试及维护工作的实际需要对示波器这样的测量仪器也提出了更多的要求,除了成本的限制以外,在体积、精度、实时性以及使用的灵活性等方面也有了更高的标准。常用的示波器一般体积比较大,成本高,这就使它的应用受到了一些限制。在这种情况下,开发低成本便携的手持示波器,将会大大提高其应用空间,为设备的外场维护和测试工作提供更多的便利。

本文针对实际需要,设计了以FPGA为核心采集模块,以单片机为显示控制核心,以TFT彩屏液晶为显示器件的便携数字存储示波器。FPGA与高速A/D获取波形采样数据,通过单片机完成彩屏的初始化,合理设计出单片机与FPGA通信的总线握手协议,配合异步FIFO作为数据缓冲模块,实现了边采集边显示的效果。该系统具有小型化、操作简单、采样率高、动态范围大、精度高、实时性强和波形显示效果连续稳定的特点,同时还具有自动频率控制和自动增益控制的功能,具有很广阔的应用空间。

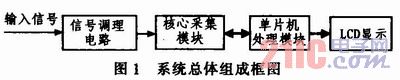

1 系统组成与工作原理

1.1 系统组成

系统主要由信号调理电路、核心采集模块、单片机处理模块和液晶外围电路组成。信号调理电路由继电器、增益控制D/A、两级可变增益放大器AD603和保护电路组成,主要用于对输入信号进行程控的衰减与放大,使信号在最佳的测量和显示量程范围内。核心采集模块以FPGA和高速A/D为核心,实现对信号的高速采样处理以及与单片机的通信。单片机处理模块接收波形数据并控制LCD进行译码显示。液晶外围电路为LCD提供合适的工作电压,并对液晶模块与单片机的接口电路进行设计。系统组成的总体框图如图1所示。

1.2 系统工作原理

根据输入信号电平的范围,FPGA发出控制信号控制调理电路的增益,将信号电平调整到最佳采集范围。在FPGA内配置两块异步FIFO作为采集数据的缓存区,实现高速采集与单片机读取速度之间的匹配。高速A/D在系统时钟的驱动下采集波形数据,并由FPGA测出信号的电压和频率。根据信号频率的不同,按照程序的预设选择最佳的时基,控制FIFO的写时钟信号,而读FIFO的时钟信号则固定不变,这样就可以在屏幕上得到最适合观察的信号波形。该系统的量程设置和时基选择完全由程序控制,不需要手动设置就可以自动将信号波形调整到最佳观察状态。

2 系统硬件设计

系统硬件主要实现对输入信号的程控衰减放大、过压保护,信号的采集处理,采集数据的传输以及单片机与液晶模块接口电路等,系统硬件总体框图如图2所示。

2.1 信号调理电路

信号调理电路实现了对输入信号的程控衰减放大,它由增益变化范围线性连续可调的可控增益放大器AD603组成。通过FPGA,结合8位D/A转换芯片CA3338E,对两片AD603引脚端的输入电压进行控制,增益和控制电压关系为:

其中,Vc1,Vc2分别表示两片AD603的控制电压。

在工作时,FPGA输出控制信号,使继电器对输入信号进行100倍衰减。衰减后的信号经A/D转换后采集到FPGA中,根据预先设置的档位判断信号所属的范围。如果信号幅度过低,不在这些范围之内,则FPGA重新发出控制信号,并减小对输入信号的衰减倍数,直到衰减后的信号满足最佳测量范围为止。对应于每个档位的信号,输出一个8位的数字信号至CA3338E芯片,并将其输出的模拟信号加到AD603的输入端,得到不同的放大倍数,完成信号的程控衰减放大。信号调理电路实现了自动增益控制的功能,有效地提高了输入信号的动态范围。

2.2 FPGA核心板模块

FPGA核心板是系统的核心,一方面负责采集并缓存数据,另一方面实现与单片机的通信。FPGA最小系统板采用的是Xilinx公司SpartanII系列的XC2S200-PQ208型20万门芯片,其配置芯片为Xilinx公司的专用配置PROM芯片XCF02S,以实现加电自动配置。核心板采用5 V输入,板上有两块LM317电源芯片分别输出3.3 V和2.5 V电压。板上采用40 MHz有源晶振,满足高速设计要求。

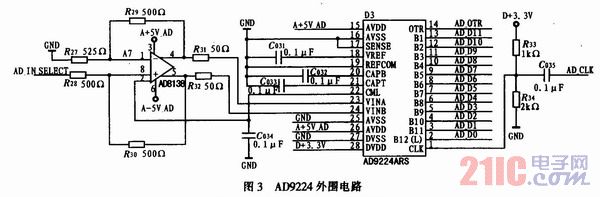

2.3 高速A/D模块

本系统选用ADI公司的12位高速模/数转换芯片AD9224,完成对模拟信号的A/D采样功能,该芯片具有极佳的动态无杂波失真范围。AD-9224的电源由+5 V的模拟电源和+3.3 V的数字电源组成。为减少A/D转换结果的二次谐波,提高信噪比(RSN),A/D芯片前端采用AD8138组成信号调理电路将单端信号转换成差分信号输入。该放大器的输入阻抗高达6 MΩ,可以直接与输入信号相连从而省略隔离放大器,因而可大大精简了电路结构。AD9224的外围电路设计如图3所示。

2.4 单片机与液晶模块接口

单片机使用C8051F020,它是一种高集成度的混合信号片上系统,有按8位端口组织的64个数字I/O引脚。液晶模块采用ILI9320片上系统(SoC)驱动器,支持26万色显示,分辨率为240 RGBx320像素,图像数据存储区的大小为172 800字节。ILI9320与MCU之间有4种总线接口方法,分别为i80系统总线、串行总线、RGB总线和VSYNC总线。本系统中采用i80总线进行控制,通过读使能(RDB)和写使能(WRB)2条控制线进行读写操作,其中数据线的宽度为8位,液晶模块中的控制信号和数据信号均为标准的TTL电平,应用时直接与单片机的GPIO总线相连。

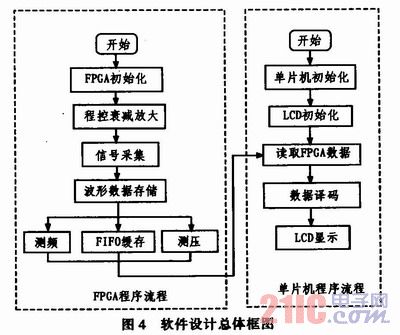

3 系统软件设计

系统软件设计主要完成对程控衰减放大电路的控制,时基的选择,异步FIFO设计,FPGA与单片机的通信协议设计,波形参数测量以及波形显示中的触发设置等。软件设计总体框图如图4所示。

3.1 异步FIFO设计

A/D采样得到采样数据的数据率很高,为了保证单片机读取数据的有效性和可靠性,系统中使用异步FIFO对数据进行缓存。FIFO的设计是通过配置FPGA内部的BlockRAM资源实现的。为了实现边采集边显示的目的,配置两块相同的FIFO,在读写时钟的控制下,通过读使能和写使能信号的设置,使得在同一时刻始终有一块FIFO在进行写操作,而另一块FIFO在将写满的数据读出。而对于同一块FIFO不允许读写信号同时有效,这样接收A/D数据和读取数据并交给单片机处理可以同时进行,从而保证数据传输的连续性。

3.2 FPGA与单片机通信的实现

FPGA与单片机之间有效的通信是系统实现正常功能的重要前提,系统中通过数据总线,地址总线和控制总线将两个模块联系起来。在FPGA中,将不同类型的数据存放到不同的地址中,这些数据包括实时采集到的波形数据,测量得到的信号参数(电压和频率),当前的时基、垂直分辨率以及一些控制参数。单片机通过地址总线对FPGA的内存进行访问,并对读取的数据做出相关的译码处理,并将处理结果实时显示在液晶屏幕上。

控制总线包括读使能和写使能信号,分别控制异步FIFO的读写操作。当其中一块FIFO中存够指定数量的采样数据以后,读使能信号有效,单片机开始接收数据,此时另一块FIFO开始写入采集数据。当数据接收完毕后,单片机向FPGA发出写使能信号,此时两块FIFO交换功能,单片机控制LCD将波形实时显示出来,并以此循环交替工作。这种异步总线握手协议的设计,使得单片机的读和FIFO的读写协调工作,大大提高了数据传输的可靠性。

3.3 波形参数的测量和触发嚣的软件实现

对信号参数的测量是示波器的重要功能,本系统可以测量输入信号的频率和电压。在FPGA内利用等精度测频技术和比较法分别进行测频和测压,由单片机通过地址线读取数据并完成数据的译码和显示。

触发器是示波器的重要组成部分,通过触发器产生的控制信号,控制示波器对波形数据的存储和显示,达到稳定同步的目的。本系统设计的触发器,采用全数字化结构,大大降低了系统硬件电路的复杂性,并且触发条件的调整比较方便。触发器通过引用单片机内部的RAM资源定制了一个采集数据的缓存区,将波形数读入该缓存区,按照预先设定的触发门限,将缓存区中的数据读出,如果满足触发条件,则将数据在屏幕上显示出来。

4 系统调试和测试

在完成了系统的硬件设计和软件设计以后,需要进行综合调试和测试。通过调试,不断优化程序代码,使系统的性能得以提高,工作状态更加稳定。在进行测试时,输入峰峰值为2 V,频率为1 kHz的正弦信号,在LCD上观察到的波形及测量参数如图5所示。从图中可以看出,波形显示稳定连续,测量信号参数的精度高,且包含彩色信息丰富。

5 结束语

研究了以TFT彩屏液晶作为显示器件的手持数字存储示波器的总体方案,即信号调理电路,核心采集模块,单片机处理模块和液晶外围电路组成。在确定总体方案的同时,给出了实现此总体方案的具体方法。

通过握手协议合理解决单片机与FPGA通信的问题,用软件设计了数字触发器,取代了一般示波器中常用的触发电路,降低了系统的硬件复杂度。该数字存储示波器允许输入信号的动态范围大,体积小,便于携带,操作简单,具有很高的应用价值和广阔的发展空间。

暂无评论