在栅极驱动器 IC 方面取得的进步让开关电源实现新的功率密度水平

简介

像许多电子领域一样,进步持续发生。目前,在 3.3 kW 开关电源 (SMPS) 中,产品效率高达 98%,1U结构尺寸,其功率密度可达 100 W/in³。这之所以可以实现是因为我们在 图腾柱 PFC 级 中明智地选择了超结 (SJ) 功率 MOSFET(例如 CoolMOS™),碳化硅 (SiC) MOSFET(例如 CoolSiC™),而且还采用了氮化镓 (GaN) 功率开关(例如 CoolGaN™)用于400V LLC 应用。PFC 和 LLC 数字控制器是必不可少,正如采用平面磁性器件和先进的栅极驱动器 IC(如 EiceDRIVER™)在实现高性能方面发挥着重要作用。

主要市场趋势

经久耐用的电气隔离

在系统的两个(或多个)部分之间必须进行接地环路隔离时,就要采用电气隔离。采用电气隔离的主要原因有:

1. 避免接地偏移(由电源开关的正常操作导致)影响系统的正常运行。

2. 防止浪涌或脉冲损害系统的完整性。

3. 保护人们免受有害电击。

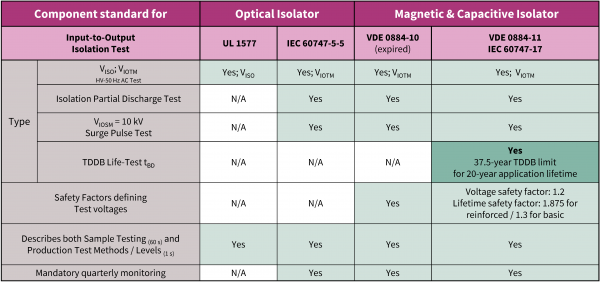

目前,德国 VDE 规范 DIN VDE V 0884-11:2017-01 (“VDE 0884-11”) 是电气隔离栅极驱动器 IC 器件级标准的“黄金标准”。

VDE 0884-11 是任何电气隔离半导体产品(即,不管是光学隔离、磁性隔离还是电容隔离)的第一个行业标准,不仅考虑了零时(即制造商测试产品时)的隔离栅特性。VDE 0884-11 还要求产品使用寿命为 20 年。为此,栅极驱动器 IC 要接受与时间相关的电介质击穿(TDDB)寿命测试 tBD(击穿时间),该测试的上限为 37.5 年(见表 1)。

而众所周知的器件级隔离标准中(如 UL 1577、IEC 60747-5-5 或同时到期的 VDE 0884-10)没有产品使用寿命的要求。

由于 VDE 0884-11 是德国标准,因此该标准已与在很大程度上类似的国际 IEC 60747-17 标准合并,IEC 60747-17 标准于 2020 年 9 月 20 日发布。

VDE 0884-11 标准中含有一个不容忽视且非常重要的声明:

“只有在安全等级范围内才能保证安全的电气隔离。应通过适当的保护电路确保符合安全等级。”

在人们需要防止触电时,这句话尤为重要。

表 1.器件级隔离标准概述

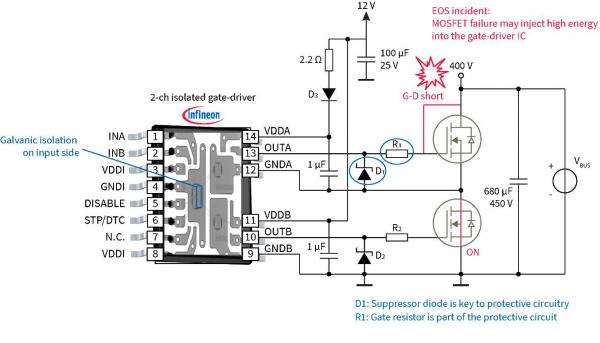

设想一下半桥中最坏的情况:高边 MOSFET 栅极-漏极短路,而低边 MOSFET 导通。在这种电气过载(“EOS”)情况下,我们可以观察到有超过 600 A 的电流流向栅极驱动器 IC 输出端。因此,为了保护栅极驱动器 IC 输出端,我们为栅极电阻 (R1) 补充了抑制二极管 (D1)(见图1)。抑制二极管为栅极驱动器输出端提供了旁路,将电流引导至半桥中点。因此,我们只要选择了合适的应用设计,那么栅极驱动器 IC 从输出端到输入端的隔离功能就能保持不变。

图1.EOS 测试装置

除了要保持这种隔离功能外,采用模塑化合物覆盖的裸露金属通常不可见,即,必须保持封装的完整性。

EOS 测试表明,栅极驱动器 IC 在 IC 输入端嵌入隔离栅后(如英飞凌科技股份有限公司的 EiceDRIVER™ 2EDR 系列),即使没有抑制二极管 D1,也能满足这两项要求。

多个进步领域

UVLO 输出级启动时间较短

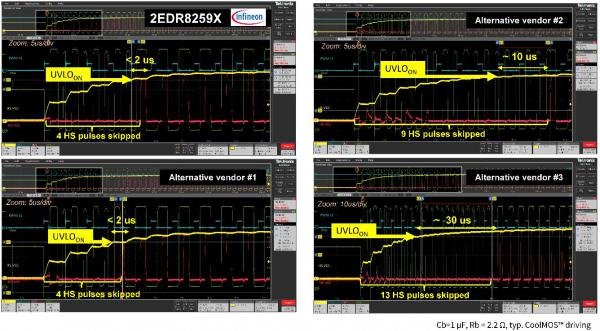

由于 高边栅极驱动器 IC 的自举电源是一种非常经济高效的解决方案,因此该解决方案很常见。因此,高压 LLC 中的 半桥 和全桥(典型值 400 V 直流总线电压),或低压 DCDC 转换器(例如,48 V 至 12 V)初级侧的硬开关全桥通常都带有自举电路。

栅极驱动器 IC UVLO 启动时间较短,从多方面为自举式设计提供了优势:

a) 快速正常系统启动。

b) 欠压保护后的 LLC 启动时间较短,例如超过 200 ms,这通常等同于 10 个电源周期。

c) 系统级保护激活后,重启释放时的 LLC 启动时间较短。

d) 在自举电路升压期间,由于高边与低边 PWM 操作不对称,主电源变压器不会出现饱和状态。

当在自举高边使用典型 UVLO 启动时间为 2 µs 的双通道 电气隔离栅极驱动器 IC 时,在半桥可以开始工作之前,只会跳过四个高边脉冲(前提是高边 VDD 上升被视为典型值)。而类似的栅极驱动器 IC,其 UVLO 启动时间为 10 µs 或更长,通常会跳过 10 个或更多高边脉冲。这就大大延长了半桥工作的开始时间(图 2)。

图2.最先进的双通道隔离栅极驱动器 IC 的 UVLO 启动时间比较

合适的 UVLO 关断时间

在达到 UVLO 触发的输出级关断时,其主要目标是能足够快地保护开关器件免受热过载。

同时,如果只是间歇降至 UVLOoff 阈值以下,则不应关断开关级。

实际经验表明,500 ns 的关断延迟是不错的选择,这可以避免 VDD 上的噪声或振铃(例如由负载跳跃引起)引发意外的输出级关断。

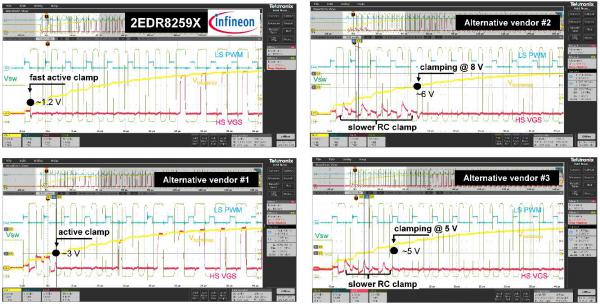

有源输出钳位

输出钳位的目的是在栅极驱动器电源仍低于 UVLOon 阈值的同时确保输出级安全关断。这降低了半桥自举启动过程中的直通风险。

在电源电压高于 UVLOon 阈值时,栅极驱动器 IC 预计会将控制输入传递到输出级,即输出端不再钳位,而是跟随输入端信号。

在自举半桥级中,当低边切换为升压电容充电时,由高边开关的 CGD 和 CGS组成的容性分压器会导致 VGS 超过其导通阈值。栅极驱动器 IC 输出钳位的目的在于避免 VGS 超过此导通阈值,并有效地使其短路。而如果输出钳位没有发生,此时高边开关与低边开关同时导通,就会形成半桥直通。

先进的栅极驱动器 IC 带有输出钳位电路,电路会在低至 1.2 V 的 VDD 电平下激活,非常适合高边开关的“教科书式”启动(见图 3)。

图3.有源输出钳位比内置 RC 钳位的输出级响应更快

与此相反,如果栅极驱动器 IC 带有内置慢速RC 钳位电路,则在半桥的启动期间会出现一定程度的直通,直到最终 VDD 值高到足以激活输出钳位电路为止。这并非理想情况,因为这会导致开关器件的电气过载。

具有可配置死区时间的直通保护

在半桥中引入死区时间的目的在于,在开关关断后、半桥另一侧导通前,使开关尾电流衰减。否则,就可能发生直通事件。超结功率 MOSFET (例如英飞凌科技股份有限公司的 CoolMOS™ )的典型衰减时间在 300 ns 内。

在正常工作的系统中,在控制器 IC 中运行的软件满足这一死时间。这样一来,控制器 IC 就可以管理该开关级的有效占空比。在确定软件控制的死区时间时,控制器 IC 硬件、操作系统和应用软件的实时性能都起到了作用。因此,基于软件的有效死区时间通常不会小于 300 ns。但在大多数情况下,这一死区时间要长得多。

为了防止基于软件的死区时间控制出现故障,栅极驱动器 IC 内置的直通控制和死区时间控制可作为第二级安全机制来防止直通事件。

现代双通道隔离栅极驱动器 IC 通过外部电阻实现了可配置的死区时间设置。死区时间从 10 ns 到 1000 ns 不等,选择空间大。因此,这种栅极驱动器 IC 非常适用于各种功率开关技术,包括 氮化镓 (GaN) 功率开关。死区时间精度可达 +/-15%。实际上,这通常比基于 IC 的死区时间控制的实际控制要精确得多。

封装创新

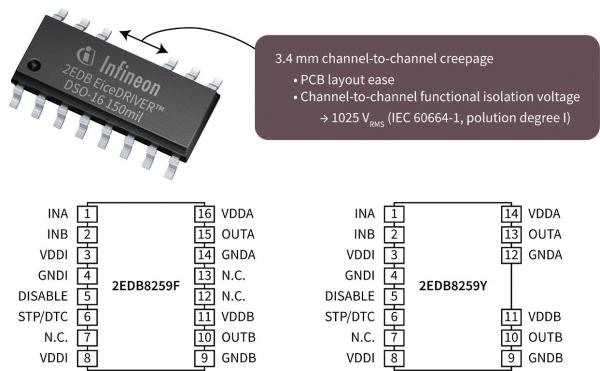

双通道电气隔离栅极驱动器 IC,采用 150 mil 和 300 mil DSO 封装,通常采用 14 引脚配置。在栅极驱动器 IC 级,传统的 16 引脚配置与越来越流行的 14 引脚配置之间的区别在于,先前输出端的“空”脚实际上已不存在(图 4)。

这样就能实现额外的 PCB 顶级布线。或者,由于由此产生的通道间爬电距离增加到了 3.4 mm(参考 IEC 60664-1,I 级污染),因此可以实现高达 1025 VRMS的通道间功能隔离电压。

电气隔离栅极驱动器 IC 的封装尺寸非常重要,设计人员现已可选用无引脚 4x4 mm2 封装。相对于默认的 5x5 mm2 封装尺寸,4x4 mm2 栅极驱动器 IC 节省了 36% 的 PCB 面积。输入输出隔离额定值相当于 VISO=2250 VRMS (UL 1577)。

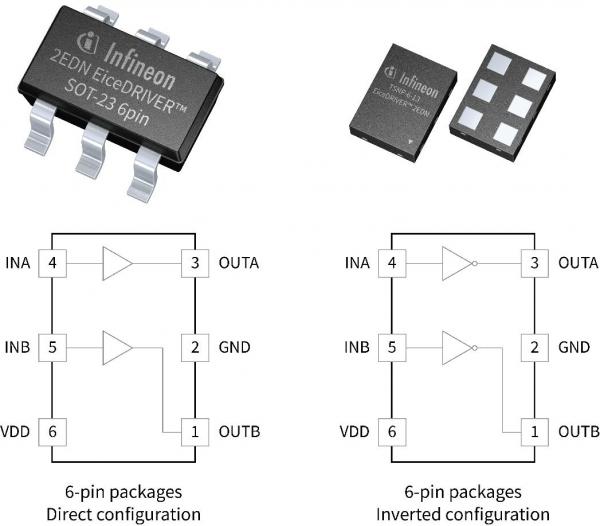

大多数现代双通道低边栅极驱动器 IC 虽然带有两个输入端,但这些输入端通常与固定电位相连,这意味着输入端实际上并未使用。那么,这种输入端存在的原因是什么,尤其是当想要实现高功率密度时?

图4.14 引脚与 16 引脚 DSO 封装比较

双通道 低边栅极驱动器 IC 采用 6 引脚封装(如有引脚 SOT-23,甚至像 TSNP 等无引脚超小型 1.1x1.5 mm2 6 引脚封装),是非常实用且经济高效的解决方案(图 5)。这样一来,栅极驱动器 IC 的所有优势都将得以体现,例如数字导通/关断特性、界定的 UVLO、5 A 强输出级、个位数 ns 传播延迟精度。同时,最大限度地降低了 PCB 面积占用,提高了 PCB 布局的灵活性。

图5.采用小尺寸封装的双通道低边栅极驱动器 IC 示例

结论

栅极驱动器 IC 集成了电气隔离,该功能已经从认证为仅在零时状态下有效的产品特征发展成为规定产品工作寿命为 20 年的产品特性。借助适当的应用设计,隔离功能和封装完整性即使在严重的电气过载情况下,也丝毫不会受到影响。

缩短 UVLO 启动时间加快了系统启动速度,也避免了主电源变压器出现饱和状态。合适的 UVLO 关断时间可防止开关器件出现热过载,还有助于在 VDD 噪声或振铃情况下保证工作稳健性。

虽然栅极驱动器电源仍低于 UVLOon 阈值,但有源输出钳位为栅极驱动器 IC 输出端提供了一条低阻抗接地路径。这种最通用的方法可以避免在自举启动过程中出现半桥级击穿事件。

栅极驱动器 IC 硬件内置可配置击穿保护和死区时间控制,这些功能是重要的二级安全机制。封装创新移除了未使用的引脚(以前称为“空”脚),而且封装尺寸也越来越小。

暂无评论